# Exploration within the Network-on-Chip Paradigm

#### Members of the dissertation committee:

Prof. dr. ir. G.J.M. Smit University of Twente (promoter)

Prof. dr. ir. Th. Krol University of Twente Prof. dr. ir. B. Nauta University of Twente

Prof. dr. K.G.W. Goossens Technical University of Delft

$NXP\ Semiconductors, Eindhoven$

Prof. Dr.-Ing. J. Becker University of Karlsruhe, Germany

Dr. R.D. Mullins University of Cambridge, United Kingdom

Prof. dr. L. Benini University of Bologna, Italy

Prof. dr. ir. A.J. Mouthaan University of Twente (chairman and secretary)

This research is conducted within the Smart Chips for Smart Surroundings project (IST-001908) supported by the Sixth Framework Programme of the European Community.

Computer Architecture for Embedded Systems group The Faculty of Electrical Engineering, Mathematics and Computer Science P.O.Box 217 7500 AE Enschede The Netherlands

Centre for Telematics and Information Technology P.O.Box 217 7500 AE Enschede The Netherlands

Copyright © 2008 by Pascal T. Wolkotte, Enschede, The Netherlands.

All rights reserved. No part of this book may be reproduced or transmitted, in any form or by any means, electronic or mechanical, including photocopying, microfilming, and recording, or by any information storage or retrieval system, without the prior written permission of the author.

This thesis was typeset in Adobe Minion Pro and Adobe Myriad Pro by the author using Late. Credit for the cover photo goes to © Galyna Andrushko – Fotolia.com. The cover was designed by the author. The thesis was printed by Gildeprint, The Netherlands.

ISBN 978-90-365-2757-6

ISSN 1381-3617, CTIT Ph.D.-thesis series No. 09-133

DOI 10.3990/1.9789036527576

# Exploration within the Network-on-Chip Paradigm

ter verkrijging van de graad van doctor aan de Universiteit Twente, op gezag van de rector magnificus, prof. dr. H. Brinksma, volgens besluit van het College voor Promoties in het openbaar te verdedigen op donderdag 15 januari 2009 om 16.45 uur

door

Pascal Theodoor Wolkotte

geboren op 16 januari 1979 te Oldenzaal Dit proefschrift is goedgekeurd door:

Prof. dr. ir. G.J.M. Smit (promotor)

# ABSTRACT

A general purpose processor used to consist of a single processing core, which performed and controlled all tasks on the chip. Its functionality and maximum clock frequency grew steadily over the years. Due to the continuous increase of the number of transistors available on-chip and the operational clock frequency, it became impossible to reach every function within the chip in a single clock cycle. Furthermore, centralized control becomes hard with the increase in functionality. This lead to the split of the processing into a set of independent processing cores integrated into a single chip.

These multi-core architectures will rely on a well designed on-chip communication architecture. Global wires and bus-based systems need to be replaced to overcome the problem of wiring and the single point of arbitration. This is introduced as the *Network-on-Chip* (NoC) paradigm. Most of the communication architectures classified as a NoC are a network of routers on-chip, but the paradigm embodies a broader scope. The paradigm enables the sharing of on-chip wiring resources for multiple communication streams to reduce the total wiring required. Furthermore, it enables concurrent communication of concurrently handled data packets. The latter is in contrast to the central arbitration and single communication channel in bus-based systems.

In this thesis we explore the paradigm by implementation and characterization of multiple NoC router architectures. The scope of the communication architecture is the embedding in a heterogeneous multi-core System-on-Chip (SoC) for streaming applications. Six streaming applications, which are used in mobile devices, are analysed. Their common communication characteristics and specific bandwidth requirements are presented. One of the major constraints of these applications is the requirement of Quality of Service (QoS) for the interprocess communication.

Based on application analysis we propose a circuit switched router architecture as opposed to a more flexible packet switched router architecture. The reason for this architecture is the observation that communication patterns in the applications are static. The circuit switched network is integrated in an ARM based heterogeneous reconfigurable multi-core SoC realized in a 0.13 µm cmos technology.

Besides this architecture, an existing packet switched router architecture, that also offers QoS, is improved and compared with the circuit switched router. Next to the exploration of those two router designs, two other packet switched routers, designed at the University of Cambridge, are included in the in-depth comparison. The four routers are placed and routed in 90 nm cmos technology. The required

buffering dominates the resource usage of all packet switched routers, which is significantly reduced in a circuit switched architecture. However, the latter pays a penalty by a larger required crossbar and reduced flexibility.

The four routers are also compared for their latency performance and energy consumption. For latency the packet switched networks are simulated with popular synthetic traffic scenarios. The circuit switched router has a deterministic latency, due to the congestion free routes.

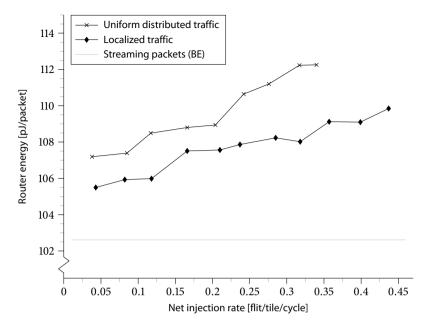

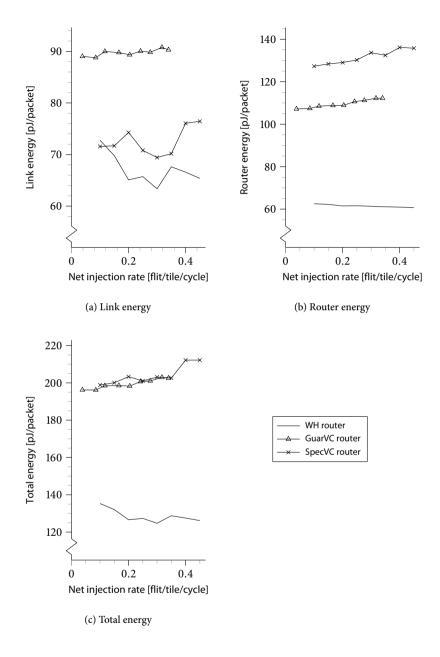

The latency analysis shows the higher network utilization for NoCs using virtual channel flow control over wormhole flow control. Furthermore, the allocation mechanisms used in the improved packet switched router, cause a higher latency for randomly distributed packets compared to the router with speculation logic that is tailored for this type of traffic. Despite its higher latency for random traffic, the packet switched network is able to give end-to-end latency guarantees for specific connections, due to deterministic arbitration, as is shown in this thesis.

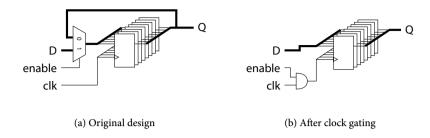

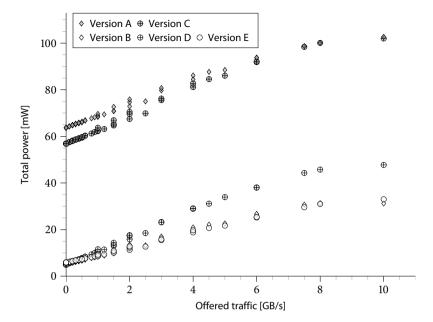

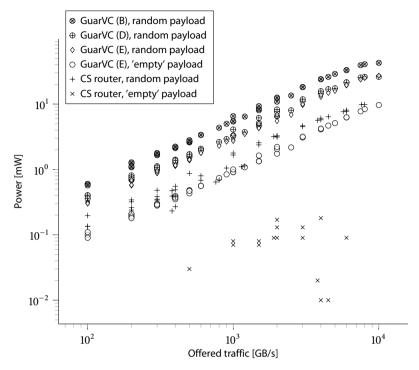

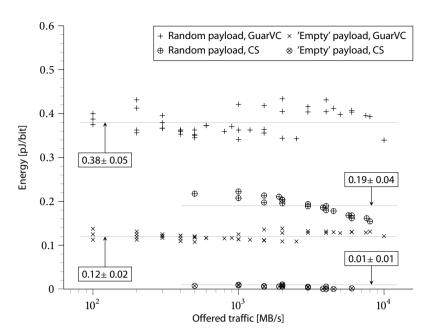

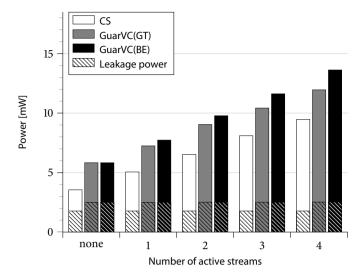

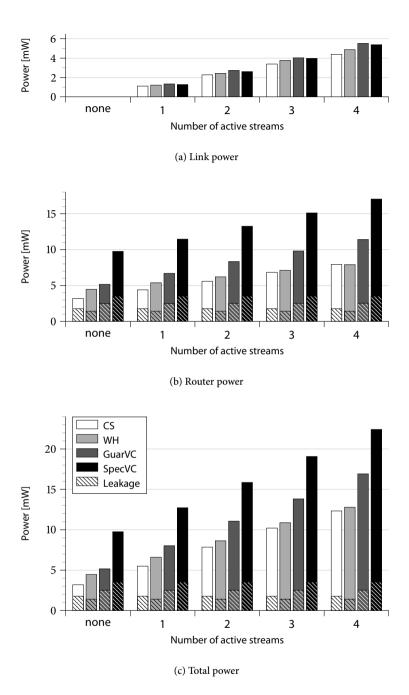

For the power analysis we compared the four routers using various traffic scenarios. One of the first observations is a high power consumption in idle mode, where no data is transported. The clock-tree and the connected synchronous elements consume the majority of the power. A minor part is the static power, which is directly related to the router's required chip area. Automatic insertion of fine-grain clock gating tremendously reduces this idle dynamic power consumption. With clock-gating, both the static and dynamic component have an equal share in the idle power at a clock frequency of 200 MHz.

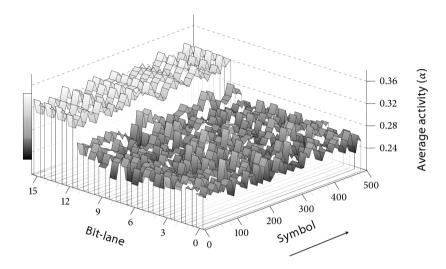

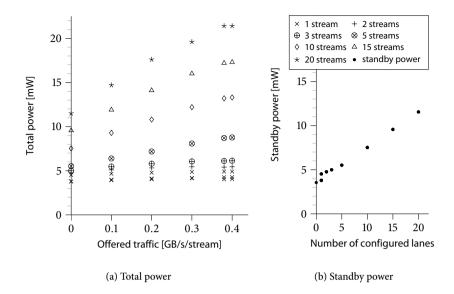

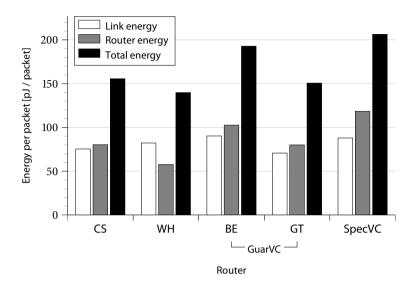

The increase in dynamic power consumption is directly related to the number of packets that are transported over the network and the amount of bit flips, i.e. activity, in the payload. Transportation of random payload, i.e. 25% activity, requires almost a factor three more in comparison with a payload of constant values, i.e. all bits inactive. Random activity is observed in the analysed streaming applications for most of the intermediate data. The buffer size has no influence on the packet's dynamic energy consumption, due to the fine-grain clock gating, which makes the packet switched routers as energy efficient as the circuit switched router. Most of the difference in energy consumption between the routers, is caused by the different crossbar dimensions and the extra bits in a packet which are required for routing and allocation. The larger crossbar is required for the circuit switched router to add flexibility, and for the improved packet switched router to enable QoS. A marginal increase in energy consumption is caused by the network congestion.

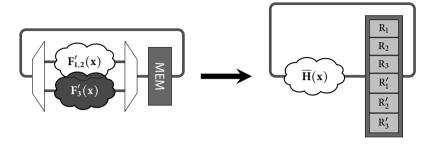

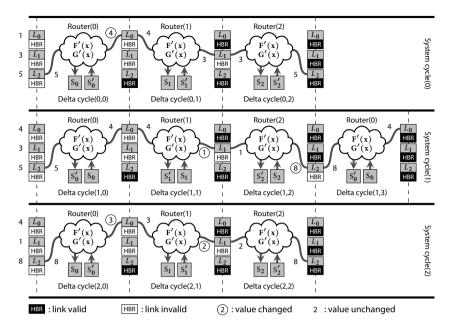

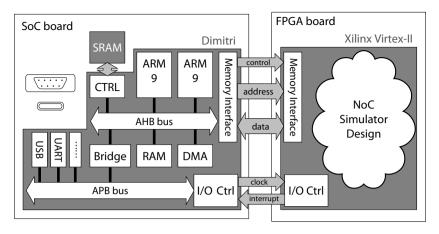

During the design of the heterogeneous SoC architecture as well as the evaluation of the packet switched routers, we were hampered by the prohibitive simulation times of the architecture's bit and cycle accurate models. Motivated by simulation speed-ups of an FPGA in a Hardware-In-the-Loop (HIL) simulation, we developed a framework to simulate large many-core architectures on a single FPGA. Instead of the instantiation of the whole architecture in parallel in the FPGA, the individual cores are evaluated sequentially. Each core is modified such that the core's internal state and combinational functionality are separated.

As all cores in a homogeneous many-core architecture are identical, we can construct a single hyper core, that embodies all combinational functionality of a

single core. The state of the whole architecture, stored in the FPGA's memory blocks, is updated sequentially by offering a core's old state to the hyper core and store its new state. Using the sequential simulation approach in an FPGA, we are able to simulate two to three orders of magnitude faster compared to cycle and bit-accurate simulations in software.

# SAMENVATTING

Tot voor kort bestond een processor op een chip uit een enkele rekenkern, die alle taken uitvoerde en beheerde. Over de jaren namen de functionaliteit en maximale klok frequentie geleidelijk toe. Door een continue toename van het aantal beschikbare transistors op een chip en de operationele klok frequentie, werd het onmogelijk om alle functies te bereiken binnen een enkele klok periode. Ook zorgde de toename van functionaliteit voor een steeds moeilijkere centrale beheersfunctie. Dit leidde tot de splitsing van een enkele rekenkern in meerdere onafhankelijke rekenkernen, die waren geïntegreerd in een enkele processor chip.

De nieuwe architectuur met meerdere kernen zal moeten vertrouwen op een goed ontworpen communicatiearchitectuur. Lange communicatiedraden en op bussen gebaseerde systemen moeten worden vervangen. Dit is noodzakelijk om problemen bij de bedrading en centrale arbitrage te overkomen. Het paradigma, dat deze systemen vervangt, is geïntroduceerd als *Network-on-Chip* (NoC). Communicatiearchitecturen die worden geclassificeerd als NoCs zijn netwerken van op de chip geïntegreerde sorteerders, maar het paradigma omvat meer. Het maakt de beschikbaarheid van de draden verdeelbaar aan meerdere communicatie stromen, zodat het totaal aantal benodigde draden gereduceerd kan worden. Een NoC staat ook simultane communicatie van berichten toe, die gelijktijdig worden afgehandeld door de beheerder. Het gelijktijdig afhandelen van berichten is niet mogelijk bij centrale arbitrage en in enkele communicatiekanaal, zoals gebruikt in bus gebaseerde systemen.

In dit proefschrift verkennen we het paradigma door de implementatie en karakterisering van verschillende NoC architecturen. De communicatiearchitectuur is toegespitst aan de hand van het gebruik in een heterogene meerkernige Systemon-Chip (SoC) voor stroom centrische applicaties. We analyseren zes specifieke applicaties, die typische gebruikt worden in mobiele apparaten. Voor alle applicaties beschrijven we de gemeenschappelijke karakteristieken en eisen en per applicatie presenteren we de vereiste communicatie bandbreedte. Een van de belangrijkste eisen, die alle applicaties stellen aan de communicatie architectuur, is de ondersteuning voor gegarandeerde service voor de onderlinge communicatie tussen de processen van de applicatie.

Gebaseerd op de applicatieanalyse stellen we een sorteerarchitectuur voor die op verbindingen sorteert in plaats van een meer flexibele sorteerder die op berichten sorteert. De belangrijkste reden voor deze architectuur is de statische communicatiepatronen in de geanalyseerde applicaties. Een heterogene herconfigureerbare

meerkernige SoC is gerealiseerd in 0.13 µm CMOS technologie, waarbij een netwerk van verbindingsgeschakelde sorteerders is geïntegreerd als communicatiearchitectuur tussen de processoren.

De verbindingssorteerder wordt ook vergeleken met een bestaande berichtensorteerder. Deze berichtensorteerder is verbeterd en ondersteund communicatie waarbij garanties noodzakelijk zijn. Naast de verkenning van deze twee sorteerders vergelijken we de architecturen ook met twee andere berichtensorteerders, die zijn ontwikkelt aan de Universiteit van Cambridge. De vier sorteerders zijn gerealiseerd in een 90 nm смоs technologie. De drie berichtensorteerders hebben een relatief groot deel van middelen nodig voor het tijdelijk opslaan van de berichten, wat niet het geval is voor de verbindingssorteerder. Deze laatste heeft daarentegen een groter schakelvlak nodig en biedt minder flexibiliteit.

De vier sorteerders worden ook vergeleken op netwerkvertraging van de berichten en hun energieconsumptie. Voor het bepalen van de berichtvertraging simuleren we drie netwerken van bericht sorteerders, waarbij we middels veel gebruikte kunstmatige scenario's berichten injecteren in het gesimuleerde netwerk. De verbindingssorteerder heeft een vaste vertraging van ingang naar uitgang, doordat conflicten tussen verbindingen niet voorkomen, en wordt dus niet gesimuleerd.

Een hogere netwerkutilisatie wordt waargenomen voor de twee NoCs die virtuele kanalen gebruiken. Door de statische allocatiemechanismen in de verbeterde berichtensorteerder veroorzaakt deze een grotere vertraging van de berichten door het netwerk ten opzichte van de sorteerder die ook virtuele kanalen toepast samen met speculatielogica. Ondanks deze grotere vertraging voor willekeurige berichten is deze sorteerder wél in staat om de vertraging van specifieke berichten door het netwerk tot een vooraf gespecificeerd maximum te beperken. Dit wordt bereikt door middel van voorspelbare arbitrage, zoals ook wordt gedemonstreerd in dit proefschrift.

De energie consumptie van de sorteerders wordt gemeten onder verschillende verkeersdruktescenario's. Een van de eerste observaties is het hoge energieverbruik, zonder dat er berichten worden getransporteerd. Het klokdistributienetwerk van de architectuur en de aangesloten synchrone elementen verbruiken het grootste deel van de verbruikte energie. Een veel kleiner deel zijn de statische lekstromen, die direct gerelateerd zijn aan de benodigde chipoppervlakte van de individuele sorteerders. Automatisch toevoegen van een fijnmazig netwerk van schakelaars, die delen van het kloknetwerk aan- of uitzetten reduceert de verbruikte energie enorm. Na toevoeging van deze schakelaars hebben, bij een klokfrequentie van 200 MHz, de statische en dynamische component van het verbruikte vermogen een gelijk aandeel.

De toename van het dynamische energie verbruik is direct gerelateerd aan de hoeveelheid berichten die worden getransporteerd door de sorteerder in het netwerk. Verder heeft de mate van variabiliteit (activiteit) van bitwaardes in een bericht invloed op het vermogens verbruik. Het transporteren van willekeurige waardes per bericht (een activiteit van 25%) vergt ongeveer drie keer zo veel energie als het transporteren van constante waardes. Een opeenvolging van willekeurige waardes is waargenomen bij veel berichten van de geanalyseerde stroming centrische applicaties. De bufferdiepte van de sorteerder heeft geen invloed op de energieconsumptie per bericht, doordat het kloknetwerk fijnmazig wordt geschakeld. Dit maakt de berichtensorteerders even efficiënt als de verbindingssorteerders op het gebied van energieverbruik. Het grootste verschil in verbruik tussen de vier sorteerders wordt veroorzaakt door de dimensies van het schakelvlak en de extra bits in een bericht, die nodig zijn voor routering en toewijzing. Het grotere schakelvlak is bij de verbindingssorteerder nodig, opdat de flexibiliteit van de architectuur toeneemt. Voor de berichtensorteerder wordt het grotere schakelvlak gebruikt om garanties met betrekking tot de vertraging te kunnen geven. Opstopping van berichten in het netwerk heeft maar een kleine invloed op de energiekosten per bericht.

Tijdens het ontwerp van de heterogene SoC architectuur en bij de evaluatie van de berichten sorteerders worden we belemmerd door de ontzettend lange simulatie tijden van de architectuur met behulp van bit- en klokperiodeaccurate modellen. Om deze simulatie tijden te reduceren is er een raamwerk ontwikkelt die het simuleren van grote meerkernige architecturen mogelijk maakt op een enkele FPGA. We zijn hierbij gemotiveerd door de tijd reductie die we eerder behaalden bij een FPGA in een Hardware-In-the-Loop (HIL) simulatie. In tegenstelling tot de instantiatie van de gehele parallelle architectuur, evalueert de FPGA de individuele kernen sequentieel. Per kern scheiden we de combinatorische functionaliteit van elementen die de toestand van de kern beschrijven.

In een homogene meerkernige architectuur zijn alle kernen identiek. Daarom kunnen we een hyperkern maken, die de gecombineerde functionaliteit van de kernen omvat. De complete toestand van de parallelle architectuur, die is opgeslagen in de interne geheugenblokken van de FPGA, wordt sequentieel vernieuwd door de oude toestand van een individuele kern aan te bieden aan de hyperkern en de nieuwe toestand in het geheugen op de slaan. In vergelijking tot bit- en klokperiodeaccurate simulaties in software, is de gerealiseerde sequentiële simulatieaanpak in een FPGA twee tot drie ordegroottes sneller.

### Dankwoord

Hier beginnen we dan met de laatste zinnen van dit proefschrift. Bijna klaar. Klaar met het afsluiten van vijf jaar werk. Toch is het proefschrift niet af zonder het bedanken van alle mensen die direct of indirect hebben bijgedragen aan mijn fantastische tijd als promovendus op de universiteit.

Het begon allemaal vlak na mijn afstuderen met een bezoekje aan de Zilverling. Gerard Smit wist erg enthousiast te vertellen over het onderzoek in de groep en zijn idee over mijn inmiddels afgeronde onderzoeksopdracht. Met een erg goed gevoel ging ik naar huis en dat doe ik nog steeds elke dag. Een promovendus in onze groep staat echter niet alleen. Zo wil ik graag de volgende mensen van de groep in het speciaal bedanken voor alle hulp.

Allereerst mijn promotor, Gerard Smit. Hij is een begeleider zoals je hem in het ideale geval zou wensen. Je laat een probleem vallen en de volgende dag heeft hij al weer een suggestie, waar je mee verder kunt, uitgewerkt. Hij voorziet papers sneller van commentaar, dan dat je de papers kunt schrijven. Hij kan ontzettend enthousiast vertellen over al het werk in de groep. Ook is hij niet vies van weddenschappen afsluiten over oplossingen die wel of niet zouden kunnen, met als gevolg dat je weer eens een nachtje slaap mist. Maar ook zeker niet onbelangrijk, hij voorzag onze vele uitstapjes voor het 4S project van de nodige gezelligheid, die ik niet snel vergeet.

In het 4S project werkte ik samen met Lodewijk Smit. Hij hielp me op weg in het prille begin met allerlei zaken: discussies over de de richting van mijn onderzoek, kritische — voor je gevoel soms te kritisch — opmerkingen en vragen over mijn oplossingen. Zelfs na het oprichten van het bedrijf Recore Systems bleef hij geïnteresseerd en behulpzaam.

In heb begin heb ik ook veel hulp gekregen van zijn kompanen bij Recore, Paul Heysters en Gerard Rauwerda. Gerard bedankt voor alle hulp bij het begrijpen van de wireless applicaties. Paul bedankt voor de discussies over architecturen, energie metingen en het leuke excuus voor de vakantie naar Aruba.

Ook wil ik in het speciaal Philip Hölzenspies bedanken. Eén dagje kwam ik gebruik maken van een vrij bureau op je koele kamer en inmiddels zijn we de afgelopen 3 jaar al weer kamergenoten. Philip erg bedankt voor alle subtiele dwang voor en hulp bij het gebruik van Vim en Linux, het beantwoorden van alle vragen over LTEX, discussies over technische en zeker ook de veel minder technische zaken, hints bij alle illustraties en presentaties, het lezen van mijn papers, en alle ondersteuning bij het schrijven van dit proefschrift.

Ik kon ook nog van veel meer kanten hulp en steun verwachten. Ik wil daarom

bedanken: André, voor het grondig lezen en corrigeren van mijn proefschrift, Bert, voor alle hulp met VHDL en synthese, Pierre, voor een goede introductie in real-time systemen, Nikolay, voor de introductie in het NoC paradigma en de discussies over onze netwerkarchitecturen, Jan, voor het helpen en oplossen van mijn toggle-rate vermoeden, Marcel, voor de leuke samenwerking in het 4S project, Albert en Bas, voor het maken van de MPEG-4 demo op het BCVP, de secretaresses, Marlous, Nicole, Thelma en Tineke, voor het helpen bij al de niet technische zaken, Jochem, voor de discussies over de FPGA simulator en de design flow, Tjerk, voor implementatie van de DDC. Als laatste, maar zeker niet het onbelangrijkste, iedereen van de CAES groep. Bedankt voor de geweldige sfeer zowel tijdens als na werktijd.

Ook buiten de groep wil ik graag een aantal mensen bedanken. Allereerst iedereen die in het 4S project heeft meegeholpen aan de realisatie van de Annabelle Chip. Het is geen ontwerp van een enkel persoon, maar het resultaat van 4 jaar samenwerking. Ik wil ook graag Arnab Banerjee van de Universiteit van Cambridge van harte bedanken. Voor al zijn metingen, de hulp bij mijn energie metingen van de routers en de discussies over de zee van getallen. Daniel Schinkel wil ik graag bedanken voor alle discussies over links en draden in cmos technologie. Ook wil ik mijn commissieleden bedanken voor de feedback op mijn proefschrift en alle gesprekken tijdens eerdere ontmoetingen op conferenties en bijeenkomsten. Voor de indirecte hulp bij de vormgeving van mijn proefschrift wil ik graag Robert Bringhurst bedanken die me via zijn boek [23] een stuk wijzer heeft gemaakt over typografie. De illustraties in het proefschrift hadden er heel anders uitgezien zonder Till Tantau en Christian Feuersänger met hun werk voor TikZ.

Tijdens mij onderzoeksperiode kon ik ook voor vier maanden naar Bell Labs in de VS. Het werk is niet opgenomen in dit proefschrift, maar vormde wel een goede opstap naar de simulator. Naast de leuke opdracht heb ik ook een erg goede tijd gehad bij Sape en Connie, waar ik een groot deel van de tijd mocht logeren. Sape en Connie bedankt voor een heerlijke ontspannen tijd en alle kookideeën waar menigeen vandaag nog van profiteert.

Een onderzoek beperkt zich niet alleen tot op het werk. Ook na het werk helpen allerlei ontspannende activiteiten. Zo wil ik iedereen die ik bij Euros heb mogen coachen van harte bedanken. Bedanken voor de geweldige ervaringen op en rond het water. In het bijzonder wil ik bedanken Guus, Martijn, Wabe, Anke, Tessa, Mauro en Sjoerd voor al die uren samen fietsend en coachend langs het kanaal, aan de bar in de kroeg en tijdens de leuke weekenden in het land.

Ook wil ik mijn paranimfen, Jeroen Harmsen en Erik Karstens, van harte bedanken. Bedanken voor alles, voor het zijn van vrienden door dik en dun en al het andere dat te veel is om hier op te noemen. Mijn broer en z'n vriendin wil ik graag bedanken voor al die zaterdagen dat ik kon helpen aan jullie nieuwe huis. Het was heerlijk ontspannend voor mijn gedachten.

Ten slotte wil ik mijn ouders en Antoinette bedanken. Bedanken voor alle hulp bij de niet technische zaken, het trots zijn op wat ik doe en vooral jullie onvoorwaardelijke steun.

## TABLE OF CONTENTS

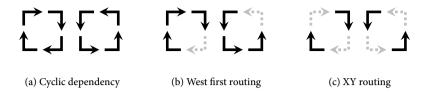

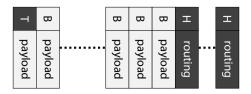

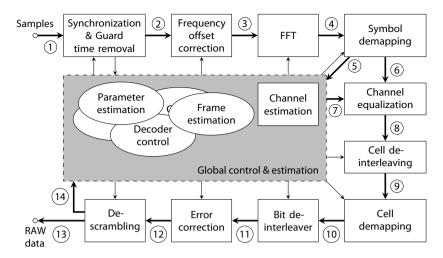

Introduction · The 4S Project · 1.1.1 Platform · 1.1.2 Applications · 5 1.1.3 Design Flow · 1.1.4 Central Coordinating Node · 7 1.2 Energy in CMOS Technology · 1.3 Design-Space Exploration · 9 1.4 Problem Statement · 10 1.5 Contributions of the Thesis · 12 1.6 Structure of the Thesis · 13 BACKGROUND AND RELATED WORK · 15 2.1 Network-on-Chip Characteristics · 17 2.2 Topology · 18 2.2.1 Torus and Mesh Topologies · 19 2.2.2 Tree Topologies · 20 2.2.3 Other Topologies · 21 2.3 Routing · 22 2.3.1 Taxonomy of Routing Algorithms · 22 2.3.2 Deadlock and Starvation · 23 2.3.3 Examples of Routing Algorithms · 23 2.4 Flow Control · 25 2.4.1 Bufferless Flow Control · 26 2.4.2 Buffered Flow Control · 26 2.5 Services · 29 2.6 Network-on-Chip Solutions · 29 2.6.1 Integrated NoC Solutions · 30 2.6.2 NoC Router Architectures · 32 2.6.3 Summary · 35 Current and Future Streaming Applications · 37 3.1 OFDM · 38 3.2 Wireless Communication · 41 3.2.1 HiperLAN/2 (802.11) · 41

3

- 3.2.2 WiMAX (802.16) · 3.2.3 UMTS · 3.3 Digital Broadcasting 3.3.1 Digital Radio Mondiale 3.3.2 Digital Audio Broadcasting · 3.4 Multimedia 51 3.4.1 MPEG-4 · 51 Common Characteristics · ROUTER ARCHITECTURES AND THEIR REALIZATIONS · Packet-switched NoC Evaluated 4.1.1 Traditional Virtual Channel Router · 4.1.2 GuarVC Architecture · 4.1.3 Implementation · 4.1.4 Synthesis Results · 67 Circuit-switched NoC Evaluated · 4.2.1 Circuit-Switching Revisited · 4.2.2 Architecture / Design · 4.2.3 Implementation · 4.2.4 Synthesis results · Comparison with other NoC architectures • 4.3.1 Wormhole Router · 4.3.2 Speculative Virtual Channel Router · 4.3.3 Packet Comparison · 4.3.4 Area Comparison 4.4 Conclusion · 82 TIMING EVALUATION · 5.1 Best Effort Traffic · 5.1.1 Improvements · 5.1.2 Other Best Effort Scenarios · 5.2 QoS and Best Effort Traffic 5.2.1 Jitter Analysis 5.3 Comparison

- Power Evaluation · 99

5.3.1 Uniform Random Traffic · 94 5.3.2 Localised Traffic · 96 5.3.3 Streaming Traffic

- 6.1 Power Estimation Techniques · 100

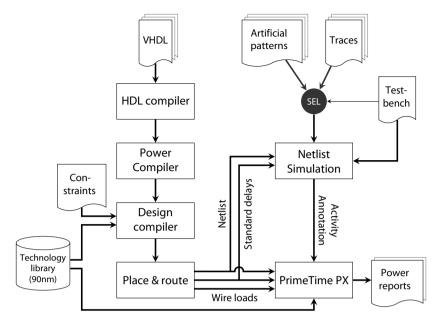

- 6.1.1 Synopsys PrimeTime PX / Power Compiler · 100

- 6.1.2 Orion · 101

5.4 Conclusion · 98

- 6.1.3 Other Methodologies · 102

- 6.1.4 Measurements by Others · 102

| 6.2 Measurement Flow                                              | · 103 |

|-------------------------------------------------------------------|-------|

| 6.2.1 Obtained Output Reports                                     | · 104 |

| 6.3 Measurement Setup                                             | · 105 |

| 6.3.1 Stimuli Generation                                          | • 105 |

| •                                                                 | · 106 |

| 6.4.1 Idle Power Consumption                                      | · 106 |

| 6.4.2 Energy Consumption Under No Congestion                      | · 108 |

| 6.4.3 Energy Consumption Under Congestion                         | • 113 |

| 6.5 Comparison                                                    | • 115 |

| 6.5.1 Energy consumption of wires                                 | · 115 |

| 6.5.2 Standby Power                                               | · 117 |

| 6.5.3 Streaming Packets                                           | • 118 |

| 6.5.4 Congestion                                                  | · 121 |

| 6.6 Conclusion                                                    | • 123 |

| - Interconstruction of a National Transfer Co.C. "Association"    |       |

| 7 Integration of a NoC in the SoC "Annabelle"                     | • 125 |

| 7.1 Architecture                                                  | • 126 |

| 7.2 Hydra: a Network Interface Design                             | • 127 |

| 7.3 Modified Circuit Switched NoC                                 | • 128 |

| 7.4 Realization of the SoC<br>7.5 Conclusion                      | • 129 |

| 7.5 Conclusion                                                    | • 130 |

| 8 Efficient FPGA-Based System Simulation                          | · 133 |

| 8.1 Related Work                                                  | . 134 |

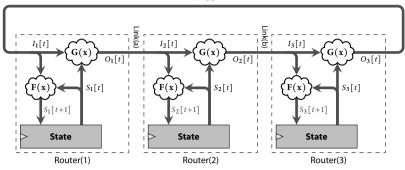

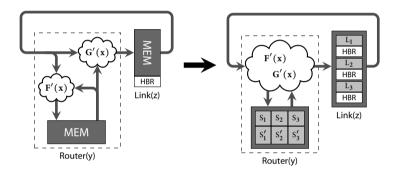

| 8.2 Simulation Framework                                          | . 136 |

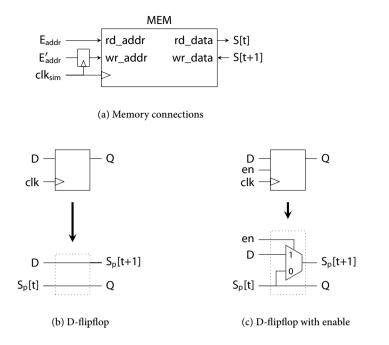

| 8.2.1 Sequential Simulation of Designs with Registered Boundaries | • 137 |

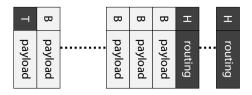

| 2 Sequential Simulation of Designs with Combinational Boundaries  | . 139 |

| 8.3 Implementation                                                | . 142 |

| 8.3.1 Platform                                                    | • 143 |

| 8.3.2 FPGA Implementation                                         | . 144 |

|                                                                   | · 146 |

|                                                                   | . 148 |

|                                                                   | . 150 |

| 8.5.1 Flexibility of the FPGA Simulator                           | . 151 |

| 8.5.2 Automated Creation of the Simulator                         | . 151 |

|                                                                   | . 152 |

|                                                                   |       |

| 9 Conclusion                                                      | . 153 |

| 9.1 Main Contributions of this Thesis                             | · 158 |

|                                                                   | . 159 |

|                                                                   |       |

| List of Symbols                                                   | · 161 |

List of Acronyms · 163

8.2.2 Sequential

#### LIST OF PUBLICATIONS · 179

A CMOS Power Consumption · 183

A.1 Power Components · 184

A.1.1 Dynamic Power · 184

A.1.2 Static Power · 185

A.2 Power Reduction Techniques · 187

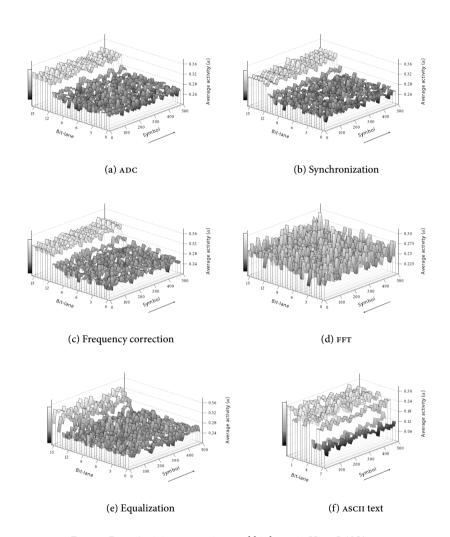

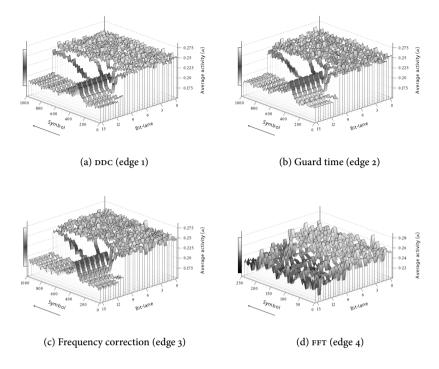

B Toggle Rates · 189

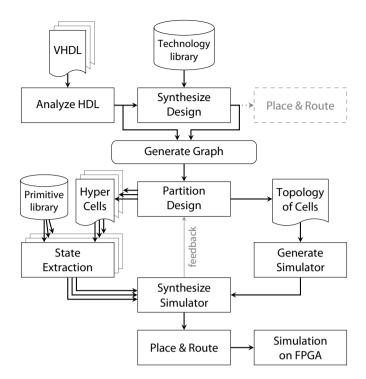

B.1 HiperLAN/II · 189

B.2 Digital Radio Mondiale · 191

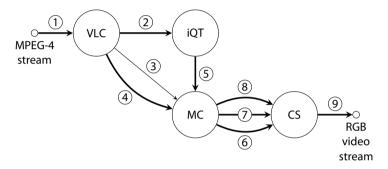

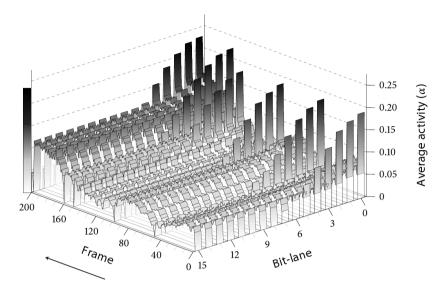

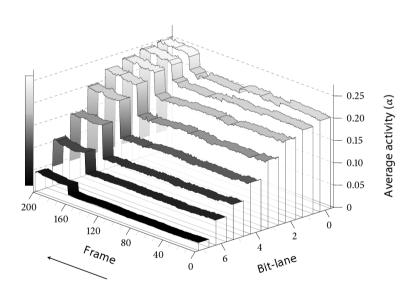

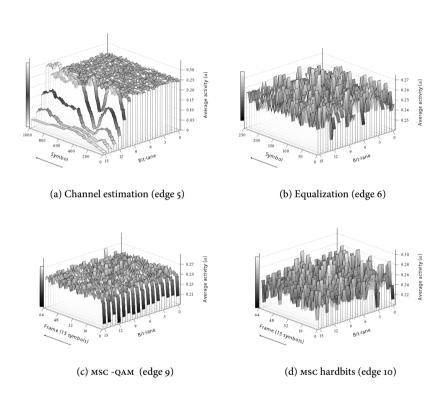

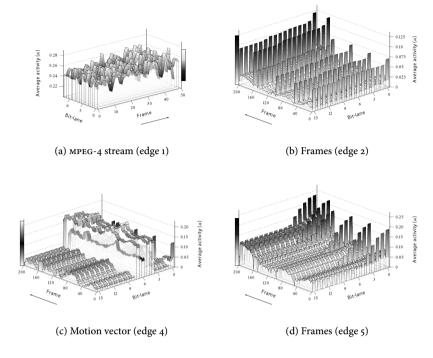

B.3 MPEG-4 · 193

C Interleaving of Packets · 195

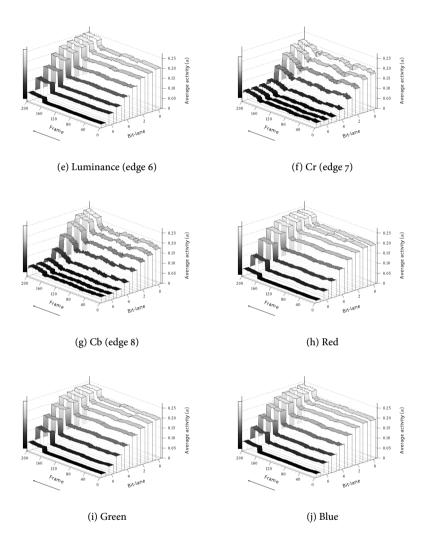

D Automated Creation of the Sequential HIL Simulator • 199

D.1 Design Flow · 199

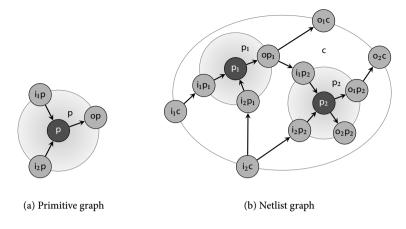

D.1.1 Netlist representation · 200

D.1.2 Partitioning of the Design · 202

D.1.3 State Extraction · 202

D.1.4 Generation of the Simulator · 204

D.1.5 Feedback · 205

D.1.6 Initial Results · 205

# Introduction

In the every day environment, people are surrounded by a large set of digital devices. The number of these devices is continuously increasing, ranging from small embedded controllers in the car, efficient processors in a mobile device to high performance processors in a laptop and desktop computer. These controllers and processors are ICs realized in CMOS technology. The continuous development of this technology enables more functionality in the same device or smaller devices with the same functionality.

It started with the first working bipolar transistor, realized at Bell Laboratories in 1947 by William Shockley, John Bardeen and Walter Brattain. Jack Kilby, working at Texas Instruments, was the first to combine transistors into an IC in 1958. Gradually more transistors were combined into an IC. This resulted in the present Very-Large-Scale Integration (VLSI) designs, consisting of billions of transistors. The performance and memory capacity of these VLSI designs has increased exponentially over the decades, mainly due to the exponential increase in the amount of transistors.

The increasing amount of transistors was initially dedicated to a single processing core to increase its functionality and the width of its data path. Such a processing core consists of a number of functional blocks. Examples of such blocks are the Arithmetic Logic Unit (ALU), a Floating Point Unit (FPU), Memory Management Unit (MMU) and Multiply Accumulate (MAC) unit. The number of functional blocks of the processing core increased, but they were controlled from a single point. The operational frequency of the processing core could increase due to the shrinking of the transistor size and an increasing number of pipeline stages.

In the last decade, this trend could no longer continue due to, among others, power and memory walls [8]. Instead multiple identical cores were integrated on a single chip, with less focus on increasing the performance of individual cores.

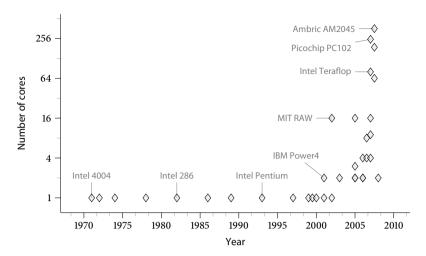

Figure 1.1 – The number of cores on a single chip, adjusted from Amarasinghe [2]

The performance of a single chip increases by adding more cores to the chip with each technology step. This trend in the number of (identical) processing cores per chip over the years is illustrated in figure 1.1 for a selection of chips. We see an exponential increase in the number of cores per chip. Some chips maintained the same functionality per core, which results in a slow increase of the number of cores per chip. Furthermore, designers created chips with a reduced functionality per core, which results in a larger number of cores per chip. With the large number of simple cores the power efficiency and amount of available parallelism on-chip increases, which is suitable for simple but highly parallel tasks.

The trend that is clearly visible with the homogeneous multi-core processors is also common practice for embedded System-on-Chip (SoC) designs. SoCs are used in, for example, mobile devices, digital radio receivers, and TV setup boxes. A SoC does not necessarily consist of a repetition of identical cores, but it may integrate a variety of modules into a single chip. The integration of, for example, some processing cores combined with hardwired modules, AD/DA converters, memory blocks and peripherals reduces the overall size of the system. A single chip solution is often more efficient in resource usage and communication between the blocks compared to multiple components on a PCB. This mix of different cores, or tiles, is often referred to as a heterogeneous multi-processor system.

With the introduction of either homo- or heterogeneous sets of processing cores per chip, extra "glue logic" is required to handle all the communication between the processing cores. The communication between two cores can be solved by direct connections. Interfaces between the cores can be chosen on a pair-by-pair basis. However, this does not scale when the number of cores increases. Furthermore, the cores have to access shared resources like for example external memory, which requires a shared communication medium. A shared communication infrastructure

creates a more flexible system in comparison with application-specific interconnects.

Similar to communication in large-scale systems, initially the on-chip architectures used bus-based communication between multiple cores. All cores are connected to a central bus and a single core can transmit a message via the bus to one or multiple destination cores. Bus arbitration is handled centrally and all nodes, which are connected to the bus, will monitor the bus simultaneously such that they receive the messages destined for them. As recognised by Guerrier and Greiner [60], bus-based architectures suffer from limited scalability and poor performance for large systems. Therefore, bus-based communication is gradually replaced by a network based infrastructure.

The on-chip communication network paradigm is introduced as *Network-on-Chip* (NoC) by Benini and De Micheli [15], Dally and Towles [38], and Sgroi et al. [118]. In the late nineties the first multi-core architectures with an on-chip network were proposed. For example, the MIT RAW architecture that connects its multiple on-chip cores via a programmable switched interconnect [132]. The individual tiles on the chip—processing cores, memory blocks, hardwired modules, etc.—are connected to one or more routers. The interconnection of routers creates a particular network topology. The NoC is a replacement for global interconnect and single bus architectures.

Despite their similarity with off-chip interprocessor communication, the trade-offs on-chip are different. In contrast to off-chip networks, the number of wires available on-chip is large, but the available buffer space is relatively scarce [38]. An IC has an enormous budget of transistors, but only a small fraction can be contributed to the NoC. Therefore, the trade-offs in buffer sizes, routing mechanisms, switch sizes etc. are different from other network routers. Furthermore, all transistors are placed and interconnected in a 2D-plane, which puts constraints on the topology of the network. Other more strict requirements for NoC architectures are the Quality of Service (QoS) demands for communication, which originate from the application constraints. The advantage of an on-chip network is the relatively controlled environment, and fixed organization of the network once the chip is realized. On-chip we also benefit from the huge amount of available wire resources in comparison with the pin limitations for off-chip communication.

In this thesis, we address a detailed exploration of the NoC paradigm. This exploration consists of the implementation, integration and comparison of NoC communication architectures. We limit the scope of the exploration to heterogeneous SoCs that are tailored for streaming wireless and multimedia applications. These applications are often used within mobile systems, where energy is a scarce resource. Research on the energy problem in mobile systems was the main motivation for the *Chameleon* project, which was later succeeded by the *4S project* and other projects. The work described in this thesis was conducted within the 4S project.

The motivation and objectives of this project are outlined in the next section. Within this thesis and the 4S project, energy efficiency is one of the optimization criteria. A short introduction is presented in section 1.2 and more details are provided in appendix A. Section 1.4 gives a more detailed description of the problem

considered within this thesis. The contributions of this thesis are summarized in section 1.5. The last section provides an overview of the structure of the thesis.

#### 1.1 THE 4S PROJECT

The overall mission of the 4S (Smart Chips for Smart Surroundings) project is to define and develop efficient (ultra low-power), flexible, reconfigurable core building blocks for future ambient systems, including the supporting tools [120, 121, 123]. As an application, the project has chosen a concrete worldwide broadcast radio application, Digital Radio Mondiale (DRM), and MPEG-4 video that can be used in an ambient system scenario.

The results obtained in the Chameleon project were one of the foundations of the 4S project [24, 122]. In the Chameleon project, the algorithms, architecture, and design of handheld multimedia systems were addressed with emphasis on energy-efficiency. Efficiency is achieved by adapting the entire platform—applications, operating system, and hardware—to the current demands of the system, which is mainly dictated by the dynamic behaviour of the mobile environment.

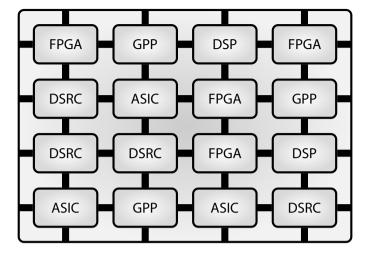

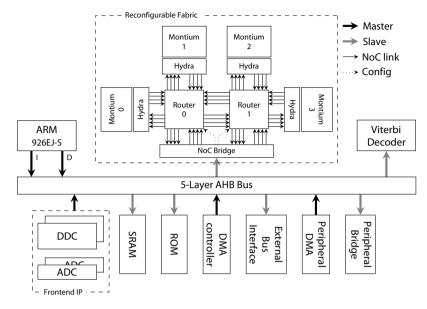

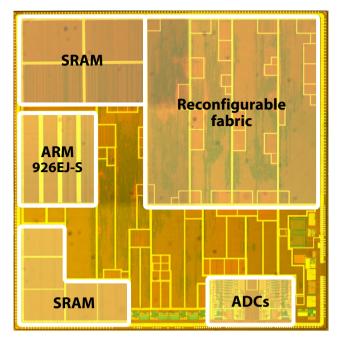

The projected hardware architecture is a heterogeneous set of processors combined in a SoC. An example of such a SoC is depicted in figure 1.2. The architecture contains a mixture of processing cores, that are each suitable for a selected range of tasks and application domains. Efficiency is obtained by assigning individual tasks of an application to the tiles that can execute the task most efficiently. For example, control oriented tasks are assigned to a General Purpose Processor (GPP) and bit-level operations to an FPGA. For this proposed template a coarse-grain reconfigurable architecture, the MONTIUM, was designed by Heysters [66], which is tailored to the digital signal processing (DSP) application domain.

At the application level, the Chameleon project studied cross-layer optimizations. By monitoring the environmental conditions like Signal-to-Noise Ratio (snr), the application can change and adapt the settings of the algorithms such that QoS is met with the minimum amount of effort, i.e. be efficient. Being efficient is achieved by Smit [124] for both Universal Mobile Telecommunications System (umts) and HiperLAN/2, by reducing the effort spent in error correction and bit error estimation when the channel conditions improve and vice versa.

Whereas the Chameleon project focussed on the design and optimization of individual blocks, the 4S project has a main focus on the integration at both the hardware and software level. The integration of hardware is realized by the design of a flexible SoC platform. On software level the design time flow is studied, such that various tools can be integrated into a single flow that enables a design time cycle of less than eight hours. The process graphs of both the MPEG and DRM applications were implemented and used to verify the design flow. Furthermore, the hardware and software are also integrated by means of run-time software. This included an operating system for the realized SoC and tools to map both MPEG and DRM applications onto this platform at run-time.

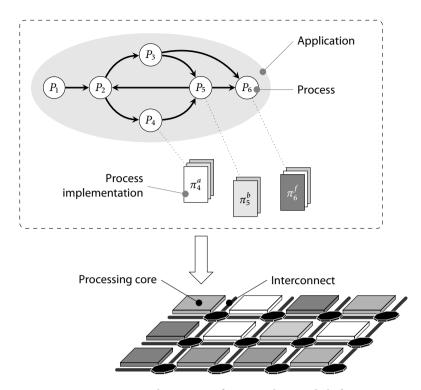

FIGURE 1.2 - Example of a heterogeneous System-on-Chip

#### 1.1.1 PLATFORM

The hardware platform, realized within the 4S project, is a *heterogeneous dynamically reconfigurable SoC*. Realization of such a platform enables us to verify the expected energy savings by assigning tasks to processors that could execute them most efficiently. Furthermore, integration of reconfigurable processing cores makes the SoC flexible enough to adapt the functionality of the SoC to the continuous evolution and adaptations of standards. In contradiction to ASIC blocks, a reconfigurable processor can adjust its instructions. This will reduce the overall design costs, because the SoC does not require an expensive re-design of the ASIC blocks in case the standard is adjusted.

Because the platform will be a heterogeneous set of processing cores, it requires an interconnection architecture. Traditional on-chip interconnect architectures quite often suffice for a small number of tiles. Within the 4S project a NoC is considered to evaluate its potential increase in performance as well as an increase in efficiency and better support for QoS compared to a bus based infrastructure.

#### 1.1.2 APPLICATIONS

Multiple applications should be able to run on the heterogeneous SoC platform. A scenario is, for example, a mobile multimedia device that can be used to listen to a radio broadcast, view an MPEG-4 encoded movie and enjoy the owner's personal MP3 music collection. These and other targeted applications within the 4S project and this thesis can be modelled as streaming DSP applications.

In streaming DSP applications, computations can be specified as a data flow graph with streams of data items (the edges) flowing between computation kernels (the nodes). These applications can be naturally expressed in this modelling

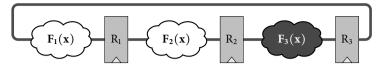

FIGURE 1.3 - Application specification and targeted platform

style [40]. A typical computational kernel, i.e. *process*, in these graphs is a mathematical algorithm, such as a Fast Fourier Transform (FFT) or a Discrete Cosine Transform (DCT). The top part of Figure 1.3 depicts an example of such a process graph. The processes in these graph will be mapped onto the processing cores and the communication channels between processes are mapped on the interconnect infrastructure.

Typical examples of streaming DSP applications are: wireless baseband processing, multi-media processing, medical image processing and sensor processing e.g. for remote surveillance cameras and phased array radars.

#### 1.1.3 DESIGN FLOW

Besides the realized platform, a design flow is necessary that enables the mapping of applications onto this platform. The flow should reduce the development time of an application and provide functions that automatically allocate the processing resources to the multiple processes of an application. The design flow is therefore split into two parts, *design-time* and *run-time*.

#### Design-Time

The development of an application is done at design-time, where an application is described as a graph of processes, as described in the previous section. Each of the processes  $(P_i)$  will have one or more process implementations  $(\pi_i^c)$  for one or more processing cores (c) on the targeted SoC (see figure 1.3). These sets of implementations are required, such that a process can be mapped on multiple processing core types that are present on the heterogeneous SoC. Per implementation, a set of performance figures is determined that is used for the mapping of processes to processing cores at run-time. The edges between the processes are annotated with the communication requirements between the processes. This can only be an average throughput requirement, but may contain extra information like message size or burst characteristics.

#### Run-Time

The mapping of the application onto the platform, i.e. choosing an implementation and a processing core for every process, is traditionally done at design-time. However, when the set of applications, the required QoS per application and the available processing cores on the platform vary over time, it results in an increasing collection of scenarios where each has its own optimal mapping. For this reason, we propose in the 4S project a design flow that performs the mapping of an application at run-time rather than at compile time. This mapping of the application is referred to as *run-time spatial mapping* and will be performed by the Spatial Mapping Tool (SMIT) [68]. Mapping determines the spatial organization of the set of processes on the set of processing cores and the distribution of the communication on the communication infrastructure. Using the performance figures, QoS and application constraints, and the available resources, the run-time mapping algorithm calculates a (near) optimal mapping. Ideally, the processes of the application will be mapped on the cores that can execute them most efficiently.

A system-wide Operating System (os), which controls the set of processing cores and their local os, instantiates the specific mapping on the system. It also adjusts the application's task graph in case of a change in the environment. The reception of a radio signal with a reduced SNR could require additional filtering, for example to suppress an interfering signal. Changing the task graph might lead to an adjustment of parameters, e.g. filter coefficients, or a complete re-mapping of the application(s), due to additional processes, by requesting a new mapping from SMIT. Re-mapping of an application can also be triggered by local failures of the hardware platform. The latter can be used to increase the fault tolerance of the system.

#### 1.1.4 CENTRAL COORDINATING NODE

With the system-wide os we assume that the SoC is organized as a centralized system. One node in the system, called *Central Coordinating Node* (CCN), performs the system-wide coordination functions. The main task of the CCN is to manage the

system's resources. It performs the run-time spatial mapping of the new applications to suitable processing cores and interprocess communications to the NoC. It also tries to satisfy QoS requirements, to optimize the resource usage and to minimize the energy consumption.

The CCN does not perform run-time scheduling of individual processes and communications while the application is executed. That is performed by the individual tiles with their local os and the network routers. The CCN only performs the feasibility analysis, spatial mapping, process allocation, and configuration of the tiles and the NoC before an application starts.

Given the fact that the architecture will have a CCN, the CCN has a holistic view of the total problem. Having a global view of the system's parameters and current state makes it possible to take better decisions. An example is QoS for two concurrently running applications. Besides a real-time scheduler on the processor(s), the communication needs to be predictable too. The CCN knows all necessary communication streams and their requirements. This can be combined with the behaviour of the routers, such that QoS can be guaranteed. For example, if a static Time Division Multiplexing (TDM) schedule is used in the routers, the CCN will assign the slots to specific streams. Knowing the slot assignment of all (successive) routers, it can optimize specific streams for latency or any other requirement.

#### 1.2 Energy in CMOS Technology

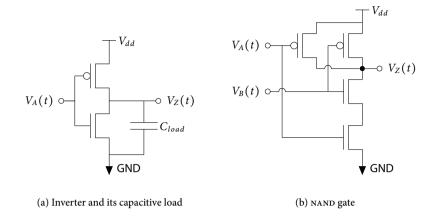

The energy consumption in a CMOS circuit design can be divided into two major power components. The first, the *dynamic power* of a CMOS circuit, is the energy that is consumed by the components when they are active, i.e. their inputs change. The second major component of the power consumption is the *static power* consumption. This is the nearly constant leakage of the circuit due to non-ideal diodes and transistors. Details on specific components of the power consumption are presented in appendix A. We present a summary in this section.

The largest part of the dynamic power is consumed due to transitions on the outputs of gates. These transitions will cause the output load capacitance of any gate to discharge or charge, which requires energy. This energy is dissipated by the resistance of the wires, but the amount energy that is dissipated is determined by the capacity that has to charged and discharged. This can be described by:

$$P_{switch} = \alpha f C_{eff} V^2 \qquad [W]$$

(1.1)

where  $\alpha$  is the activity, f is the frequency on which the circuitry operates, and V is the supply voltage of the circuitry that has an effective capacitance of  $C_{eff}$ . This capacitance includes the load of the connected wire  $(C_{load})$ , but also includes the internal capacitances of the inverter and input load of the successive gates that have to be charged and discharged as well. Although the complete circuitry has a frequency of f, the individual gates might have a reduced number of transitions. This relative reduction can be corrected via the scaling factor  $\alpha$ . A minor part of the dynamic power is consumed by the short circuit power. This part is a result of

| Generation | Year | $I_{pn}$ | $I_{sub}$ | $I_{gate}$ |

|------------|------|----------|-----------|------------|

| 90 nm      | 2004 | 25 pA    | 804 pA    | 13 pA      |

| 50 nm      | 2010 | 3 nA     | 21 nA     | 52 nA      |

| 25 nm      | 2016 | 120 nA   | 260 nA    | 510 nA     |

Table 1.1 – Predicted development of leakage in CMOs circuitry [65]

a period, during an input transition, that neither the NMOS nor PMOS transistors are in their cut-off region, which causes a short-circuit current between supply and ground rails.

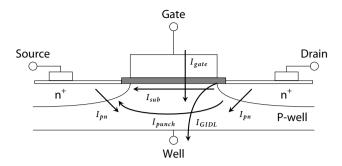

The second component of the CMOS circuit power consumption is independent of the circuit's activity. In theory the gates should not be conducting when their inputs and outputs voltages are stable, because either the NMOS or PMOS transistors of a gate are within their cut-off region. However, a leakage current ( $I_{leak}$ ) is present due to the non-ideal transistors. Multiplying this current with the supply voltage ( $V_{dd}$ ) results in the static power consumption.

When an ASIC is active at its maximum frequency, the dynamic power takes the largest share in the total power consumed. However, when a circuit is inactive, only the leakage current remains unless the supply voltage is switched off. The leakage current will increase due to technology scaling. The increase of leakage current is caused by the quickly reduced oxide thickness  $(T_{ox})$  of the transistors.

A prediction of the three major leakage currents—reverse-bias pn junction leakage  $(I_{pn})$ , subthreshold leakage  $(I_{sub})$ , and gate leakage  $(I_{gate})$ —in future generations cmos is given in table 1.1. In this table we note a rapid increase of the leakage currents. For technologies of 90nm and above the subthreshold leakage is the main source of leakage. For smaller feature sizes the gate leakage will surpass the  $I_{sub}$ .

In this thesis we will focus on techniques that can reduce the dynamic power consumption, but for future technologies it will be worth to consider leakage reduction techniques too. Were reduction of dynamic power will reduce the cost for transportation of bits, the leakage reduction will also reduce the deployment costs of the architecture. Possible techniques to reduce the overall power consumption are presented in appendix A.

#### 1.3 Design-Space Exploration

In this thesis, we study on-chip communication architectures with a primary focus on Network-on-Chip architectures. The NoC communication architectures will be used in multi-core systems.

In the design of the NoC or any other communication infrastructure for multicore architectures, designers have to make many choices. These choices have an effect on the overall performance of the NoC and on the system as a whole. To achieve a good performance, the designers have to make trade-offs between different performance parameters, e.g. operation bit-widths, memory sizes, packet sizes, operational frequency, latency, and throughput.

Exploration of communication and processing architectures, to find these tradeoffs, can be performed at various levels. In this thesis we have chosen to perform a detailed exploration by means of the implementation, integration and comparison of various router architectures. We want to compare the routers on area requirements in CMOS, communication latency, and energy consumption. Furthermore, within the 4S project, we had to realize a SoC in 0.13 µm technology.

The communication latency of a communication infrastructure can be determined, for example, by a system level simulation. A frequently used language to perform such a simulation is SystemC [102]. An example of SystemC simulation for NoC is the On-Chip Communication Network (OCCN) project, introduced by Coppola et al. [30], which defined a universal Application Programming Interface (API) for specification, modelling, simulation, and design space exploration of NoCs. The general SystemC approach, which supports any design, can also be replaced by simulators dedicated for the communication domain. For example, the OPNET modeler [101] is a domain specific simulator for network systems.

For power/performance analysis the designer can, for example, use Orion. Orion is positioned as a power/performance interconnection network simulator that is capable of providing detailed power characteristics, in addition to performance characteristics, to enable rapid power/performance trade-offs at the architecturallevel [133]. A variety of networks can be build using basic building blocks, which have been characterized for power.

All the tools, described above, have incorporated simplifications such that the design is simulated at a higher level of abstraction compared to RTL, which can be synthesized to actual hardware. The level of abstraction determines the speed of simulations. However, it also determines the level of accuracy and it may abstract from not modelled performance bottlenecks.

After an analysis of possible tools for NoC exploration, we have decided to perform the exploration at the RTL level, by designing the router architectures in VHDL. Although building components at this level is considered time-consuming, we had to the build a router module that can be synthesized anyway, because the NoC architecture had to be integrated in the realized SoC. Furthermore, router architectures and other components have to be also modelled in a language for any other exploration tool. Using VHDL, we were not limited by the availability of either power and area models, because a wide-range of accurate values are available for the characterization of standard cell libraries. Furthermore, using a single description of the architecture reduces the risk of design discrepancies.

#### PROBLEM STATEMENT

In this thesis, we study on-chip communication architectures with a primary focus on Network-on-Chip architectures. The NoC communication architectures will be used in multi-core systems.

This study consists of a detailed exploration by means of the implementation,

integration and comparison of various router architectures. Exploration of communication and processing architectures can be performed at various levels, as described in the previous section. Higher-level exploration is generally considered to have lower costs, and is therefore often the selected approach. Costs in this exploration consist of, but are not limited to, required knowledge, invested time, and required resources. However, to gain a good understanding of the hardware architecture's full potential and its problems, detailed exploration is required.

Our hypothesis is that the detailed exploration of the NoC will deliver these valuable results against acceptable costs. In this thesis we present the results of the exploration and we discuss frameworks to reduce its costs. We will conclude the thesis with a discussion of the trade-off between obtained results and their required costs.

We limit the scope of the multi-core architectures to heterogeneous SoCs that can be used for streaming applications. As described in section 1.1, we expect the heterogeneous SoC architecture to be a good candidate for energy efficient processing of streaming applications. Efficiency is obtained by assigning each process of an application to the processing core that is able to perform the required computations most efficiently and by minimizing the interprocess communication costs.

Before we propose a suitable communication architecture for these heterogeneous SoCs, we need to examine the communication requirements of the streaming applications. The first objective in this thesis is to quantify the communication requirements of typical streaming applications. Six applications are selected for this analysis. Furthermore, we want to identify their common and different characteristics.

Based on these requirements and characteristics, we can design a communication architecture that is suitable for streaming applications. We want to evaluate and compare implementations that can be directly integrated and realized in silicon. Therefore, we discuss implemented on-chip communication architectures. This is a different level of evaluation compared to a higher level model-based approach, which enables a broad exploration of the router's design space. In this thesis we focus on the design of the communication architecture such that it can be integrated into a SoC that can be realized in silicon. The experience gained with actual implementations of the architecture will give important additional insights which can be used to refine the higher level models. These models can be used by others for their coarse and wide design space explorations.

Besides the actual embedding of the communication architecture in a real system, we also want to measure its performance and compare it with other architectures by objective and simple measurements. We will discuss possible performance measures to evaluate the router architectures. With a selection of possible measurements we compare the proposed communication architectures with router architectures implemented at the same level of detail. This detailed analysis of the router's performance will result in a large number of measurement results. We want to extract a simple model that summarizes the performance of an architecture and can be used in larger system models. These large system models are, for example,

used by design space exploration tools and the spatial mapping tool, see section 1.1.3. The latter tool requires a simple model for the cost of the communication and processing of data to determine where to map each process on the SoC.

During the design of a large SoC, we noticed that, after design space exploration and the selection of blocks to realize the SoC, a considerable simulation effort is required. Primarily, this effort was spent during the integration of the individual blocks into a larger system, which requires the actual architecture description in a Hardware Description Language (HDL). Where design exploration for SoC can be done at various levels of abstraction (and languages), the simulation of the final integrated system requires the same design sources as used for the chip that is realized. This last simulation helps to find errors, overlooked in the previous design stages, and will give extra confidence in the chip just before tape-out. Furthermore, it gives the possibility to extract data traces that can be used for detailed profiling of the architecture's performance and energy consumption. However, due to the large amount of detail, software based simulation results in prohibitive execution times. The benefit of detailed information and disadvantage of long simulation times, resulted in the last topic that is addressed in this thesis.

We examine the possibility to use an FPGA in a Hardware-In-the-Loop (HIL) based simulation approach. We expected that this could result in a considerable decrease in execution times for the cycle and bit-accurate simulations. However, an FPGA has limited hardware resources. We propose and evaluate a framework to overcome these spatial restrictions and simulate large multi-core architectures. We use the original design sources, which are used to synthesize the SoC. These are transformed in such way that a considerable decrease in resource usage is obtained, but still a large increase in simulation speed compared to software based simulations is obtained.

With the answers to the above questions in this thesis, we want to give more detailed insights in the trade-offs that are made when designing the communication architecture for multi-core platforms.

#### 1.5 CONTRIBUTIONS OF THE THESIS

Contributions of this thesis are made in different areas. First, we perform an exploration of a range of streaming applications and their communication requirements. These applications are mapped to heterogeneous SoC architectures, which gives insights in the detailed communication requirements. We present the process graphs of these applications in combination with the required communication bandwidths for the individual edges. Besides the bandwidth requirements we analyse the content of the individual data streams of three applications. The content of the packets gives information on the toggle-rate statistics, which has a direct influence on the power consumption of the communication architecture.

Second, we propose a circuit switched NoC architecture that was motivated by some of the common characteristics found during the application analysis. Together with this circuit switched architecture, an existing packet switched router is improved and examined in detail.

Third, both NoC architectures are analysed with respect to their performance in area requirements and energy consumption. For the packet switched router, we also measured the network latency under various traffic conditions. These results are compared with the performance of two other NoC architectures. For area and latency comparison, existing metrics are used and we extend the latency measurements with scenarios to test QoS traffic types. For the energy consumption, we propose a number of tests that can be applied to a router, such that its capability to transport various types of traffic can be characterized.

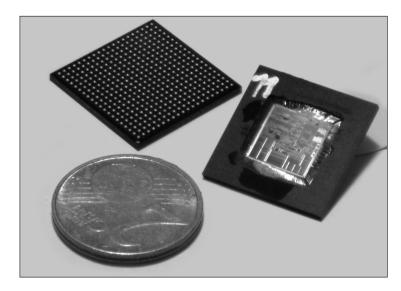

Fourth, the circuit switched router alternative was selected and implemented for a SoC with four processing cores. The heterogeneous SoC is realized in 0.13  $\mu$ m technology. For a small network of processing cores, the circuit switched alternative is selected and implemented for a SoC that is realized in 0.13  $\mu$ m technology.

The last contribution is a new framework to perform fast bit and cycle accurate simulations of multi-core architectures. Instead of a software based simulation, the multi-core architecture is mapped onto an FPGA, resulting in a HIL-based simulation. The multi-core architecture is transformed such that the number of required FPGA resources is drastically reduced. The parallel multi-core architecture is simulated sequentially, core-by-core, on this FPGA-based Sequential Hardware-Inthe-Loop Simulator (SHILS). The SHILS performs bit and cycle accurate simulations of hardware designs without prohibitively long simulation times that are common in software based simulators. The framework is applied to the improved packet switched router architecture, which enables a thorough analysis. Where others present only average results, this framework enables the designer to obtain more detailed characterization of the simulated architecture.

#### 1.6 STRUCTURE OF THE THESIS

In this chapter, we described a trend that is clearly visible in the general purpose processing architectures realized in CMOs technology. This trend is a gradual shift from a chip with a single powerful processing core to a chip with a (large) homogeneous set of processing cores. For SoCs, we also see a shift from a single processing core with some peripherals and small hardwired specialized blocks directly controlled by this single core, to a heterogeneous set of cores which can run autonomously. For both types of architectures, due to the increased parallelism, the communication between the processing cores must be addressed. Network-on-Chip is an approach to improve the performance of this communication and will be the focus of this thesis. A further introduction of the concept and related work to this thesis is described in chapter 2.

We limit the scope of the processing architectures to heterogeneous SoCs for streaming applications. A selection of these applications is discussed in detail in chapter 3. Based on the requirements, we propose a circuit switched router and improve the realization of a packet switched router in chapter 4.

The performance of the routers is evaluated on area requirements, network

latency, and energy consumption in respectively chapters 4, 5, and 6. The evaluation is performed by varying the parameters, e.g. data path width, network load and switch activity. For a selected number of tests the two routers are compared with two other realizations of NoC routers.

Chapter 7 presents the realization of a small on-chip network in a SoC realized in CMOS technology. The long simulation times for the initial network latency analysis and the SoC integration tests were two major motivations for the development of a faster simulation approach for multi-core architectures. The new FPGA-based framework and realized SHILS are presented in chapter 8. In chapter 9, some conclusions and suggestions for future work are given.

# CHAPTER

# BACKGROUND AND RELATED WORK

ABSTRACT – The NoC is a specific flavour of interconnection networks. Interconnection networks have been studied for more than two decades and a solid foundation of design techniques is available. We will give a short introduction to the terminology, principles, theory of interconnection networks that are relevant for this thesis. Furthermore, we describe specific characteristics of NoCs in comparison with networks in general. We also present some NoC solutions and present the techniques they employ.

In this chapter we describe the basic principles of a NoC and present some examples of NoC architectures. The NoC is a specific flavour of interconnection networks. According to the definition given by Dally and Towles [39], an interconnection network is a defined as: "A programmable system that transports data between terminals." A terminal refers to a general block that generates data for or consumes data from other terminals. This definition of an interconnection network occurs at many scales. For example, networks to interconnect on-chip local memories, registers and arithmetic units in a single processor, networks to interconnect processors and memories on PCB and racks, and finally local-area and wide-area networks that connect systems in a building or across the globe. The NoC interconnects the various components of a single VLSI architecture. These components can be small arithmetic units, but most of the NoC studies focus on the interconnection of processing cores and large on-chip memories. The NoC transports data that is communicated between those components and we refer to the combination of the NoC with the components as a *System-on-Chip* (SoC) architecture.

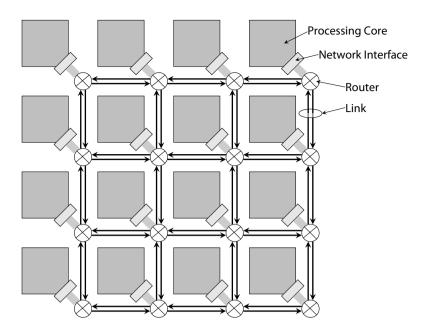

Figure 2.1 depicts an example of a SoC architecture to illustrate the major components for the global on-chip communication. Throughout this thesis we will

FIGURE 2.1 - Example of a 2D mesh topology NoC

use the following description of the four basic components:

CORES in a SoC architecture are the producers and consumers of data transported by the NoC. A core contains for example of a processing core, hardwired macro, memory module, or another Intellectual Property (IP) block.

Network Interfaces decouple the computation of the cores from the communication of the network. The Network Interface (NI) implements the interface between network protocol and the protocol(s) supported by the core. Furthermore, it also is a physical interface, which allows different clock and voltage domains for the network and the cores.

ROUTERS handle the network packets according to the chosen network protocol. The packet's items can be buffered in the router and forwarded via the links to the successive router along the packet's route.

Links connect the router nodes and provide the raw bandwidth. They may consist of one or more logical or physical channels. They usually consist of two unidirectional data channels each accompanied with additional control wires both in forward and backward direction. The control wires enable, for example, multiplexing of logic channels onto a physical channel and back pressure to prevent buffer overflow in the successive router. In this thesis we consider all links to be symmetric, i.e. data can flow in both directions via unidirectional channels.

The figure illustrates a specific instance of 16 routers organized in a  $4\times4$  two dimensional mesh, where each router interfaces with a single processing core and its neighbour routers. A wide variety of other organizations, i.e. topologies, is possible, for example, a single router connects to multiple cores or each router connects to exactly two neighbour routers such that a ring structure is created.

In general we consider the cores and network interfaces to be the *terminals* and the routers, i.e. *routers*, together with the links the *interconnection network*. This interconnection network, from now on referred to as network, is primarily defined by its topology and its protocol. The *topology* defines the layout and connections of the routers and the links of the network. The *protocol* specifies the use of the routers and links. The protocol separates two strategies—routing and flow control—to handle the network data. Furthermore, the network protocol can offer traffic specific services. In section 2.1 we describe specific characteristics of NoCs in comparison with networks in general. In the sections 2.2 to 2.5 we present an overview of possible topologies and protocol strategies for NoC architectures. In section 2.6 we present some existing NoC solutions. In this chapter we only provide the information that is relevant for this thesis. For a more detailed overview of possible topologies and protocol strategies we refer to two books by Dally and Towles [39] and Duato et al. [47], and a NoC specific survey by Bjerregaard and Mahadevan [20].

#### 2.1 Network-on-Chip Characteristics

Before we present the basic techniques of an interconnection network we present some specific criteria and requirements for a NoC as depicted in figure 2.1. The NoC is similar to Multi-Processor (MP) networks used to interconnect multi-processor systems. These networks interconnect chips on a PCB or multiple boards in a rack, where as the NoC is integrated on-chip.

The inter-chip and inter-board communications requires signals to go off-chip via pins. Therefore, these networks are heavily bounded by the number of pins of a package, which is limited. Furthermore, an increasing number of pins are grouped in pairs, such that more robust differential signalling can be applied. In contrast with this the NoC can use the large amount of wires available on-chip. Although only a fraction of the wire resources can be used for global communication, the amount of wires is still large. For example, in 65 nm technology the minimum global wire pitch equals 210 nm [74], which enables to bundle thousands of wires crossing an edge of 1 mm length. In comparison, the latest Ball Grid Array (BGA) packages have a pitch of 0.3 mm [77].

One of the limitations of a NoC is the relative small chip area available. The NoC is part of the SoC that is realized on-chip. The largest portion of the chip should be devoted to the computational and memory resources and only a small fraction to the NoC. The NoC's area requirements should be up to 5–10% of the total chip area [20, 38]. For a 0.13 µm processing core the average size is between the 2 mm² and 4 mm² [20, 66]. We assume that a single processing core is accompanied

by a single router, such that a router should have an average size of approximately 0.2 mm<sup>2</sup>. Furthermore, due to this small area requirements, the available area for buffering is small.

Another requirement that is different from large MP networks is the layout of the NoC in a 2D plane. The organization of the various modules on-chip is inherently two dimensional, where as the inter-connection and organization of processing boards in a MP system can be three dimensional. Furthermore, the positioning of the individual routers determines the layout of the links between them. Each link will contain a large bundle of wires, which will be positioned in the higher metal layers, because they span over a longer distance. A topology that is inherently regular and can be layout with structured and short links is therefore preferred. It will also reduce the verification costs in comparison with a irregular topology. The layout of those links should be handled with care, such that the signal integrity problems are prevented. The signal integrity problems of structured links can, for example, be solved by shielding, differential signalling and twisted pairs [92].

As described in chapter 1, the number of processing cores increases with the shrinking size of the transistors on a chip. The increasing number of processing cores per technology step will also result in larger network sizes. This continuous scaling requires a scalable network design, such that the communication networks of smaller technology nodes can be implemented with existing router designs.

At the service level of the network a major difference between MP networks and NoC is the need for QoS. Traditional multi-processor systems were focussed on the high performance of the whole system. A NoC is, for example, applied in systems that perform the required processing for time critical streaming applications. For example, applications in mobile phones and TV setup boxes. Those applications require QoS such that the phone call is not interrupted and the frame rate of the video decoding is met.

#### 2.2 Topology

The topology of a network describes the interconnection of the routers by the links. The chosen arrangement determines the possible and efficient protocol strategies implemented by the routers. Furthermore, the organization of the routers influences the positioning of the terminals. In case of a *direct network* this influence is strong, because these types of networks have at least one terminal connected to each router. In contrast, a network where not every router is connected to at least a terminal is called an indirect network

The organization of routers can be described as a graph, where routers are the vertices and links the edges of the graph. This model does abstracts away from implementation issues, for example a major constraint for a NoC is the placement of the routers in a 2D plane.

With this graph representation, each topology can be characterized by a few properties. The *degree* of a router is the number of links connecting that node to its neighbour vertices. A topology is considered regular when all routers have the same

degree. The *diameter* of the network is the maximum distance between two vertices in the network. Large diameters will result in a higher latency for the messages transported by the network.

A network can grow in multiple dimensions if the number of routers increases. This will result in a faster growth of required wiring resources in comparison to the increase of routers. A measure to quantify these wiring costs is the *bisection width* of a network—the minimum number of wires that must be cut when the network is divided into two equal sets of nodes. We assume that each link in the network has *W* wires that carry data bits. The *bisection bandwidth* is the collective bandwidth of the wires carrying data on those links. Although a larger bisection bandwidth requires more wiring resources, it offers a higher bandwidth to the terminals interconnected by the routers.

Another measure that is somewhat related to the bisection is the *connectivity*. A network is called k connected if there exist maximally k internally vertex disjoint paths between any pair of vertices. This measure describes the path diversity between the nodes, and therefore can be used to quantify the fault tolerance of a specific topology. With the increase in the number of paths between a pair of nodes, it also is a measure for the performance of the network similar to the bisection bandwidth.

#### 2.2.1 TORUS AND MESH TOPOLOGIES

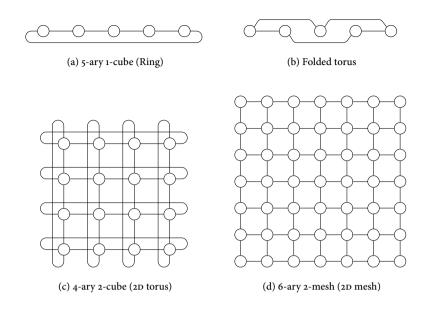

A simple way to describe a large set of regular network topologies is by a k-ary n-cube, or torus network, where k is the number of nodes per dimension and n the number of dimensions, as introduced by Dally [33]. The k-ary n-cube networks connect  $N = k^n$  nodes in a regular grid. The bisection width of a k-ary n-cube equals  $2Wk^{n-1}$  and the diameter is  $n \mid k/2 \mid$ .

The topologies that are considered for NoC architectures most often are those with low dimensions due to placement of the routers in a 2D plane. Examples of those networks are a ring, with n=1, and the 2D torus, with n=2 as depicted in respectively in figure 2.2(a) and figure 2.2(c). A disadvantage of any torus network is the unequal length of the links when the routers are positioned in a 2D plane.  $k^{n-1}$  links wrap around from one edge of the network to the opposite edge. To overcome this problem we can reorganize the positioning of each element, such that a folded torus is created where each link has approximately the same length. Figure 2.2(b) depicts the reorganization of the ring network of figure 2.2(a), which can also be achieved for the 2D torus network of figure 2.2(c).

A variation of the torus networks are mesh networks where the wrap around links are removed as illustrated in figure 2.2(d). For a 2D mesh it simplifies the layout of the links in the 2D plane, but the symmetry of the torus is removed. This can cause load imbalance, as the load on the central links will be in general higher in comparison with the load on links at the edge of the network. Compared to the torus network, the mesh network has the same node degree, but half the bisection bandwidth and the diameter is twice as large.

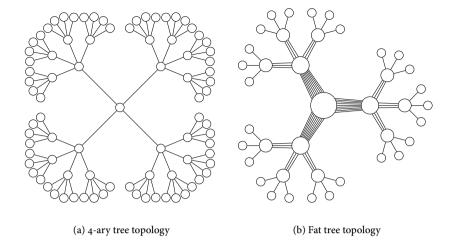

For mesh and torus networks it is assumed that each router in the network is

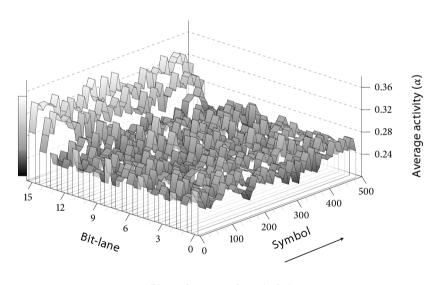

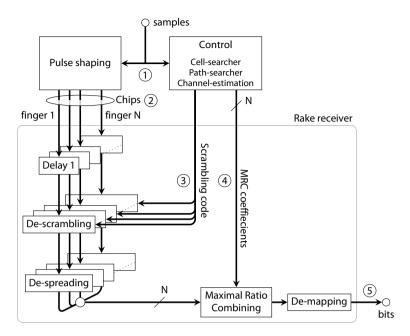

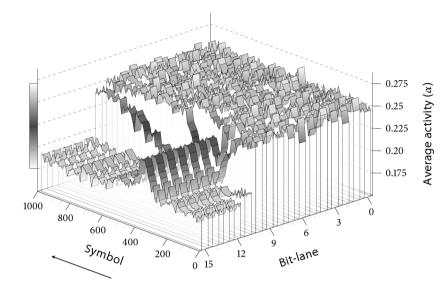

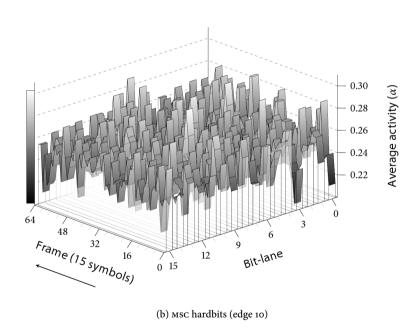

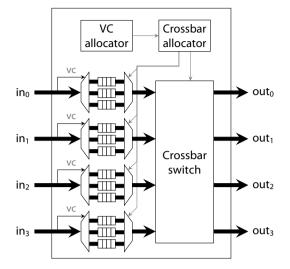

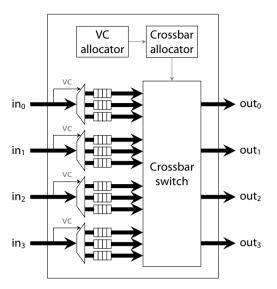

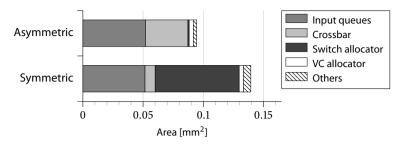

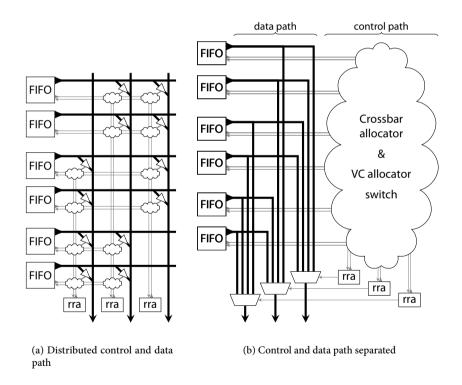

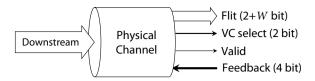

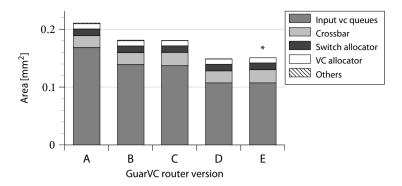

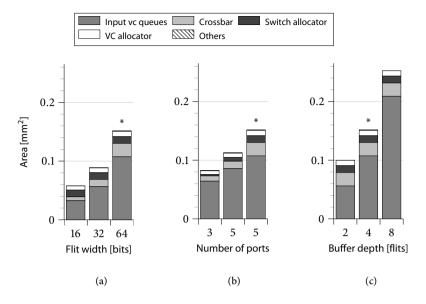

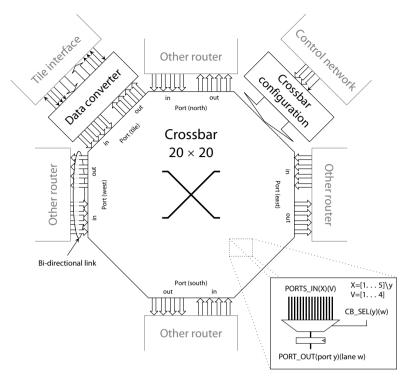

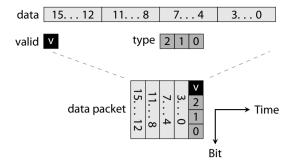

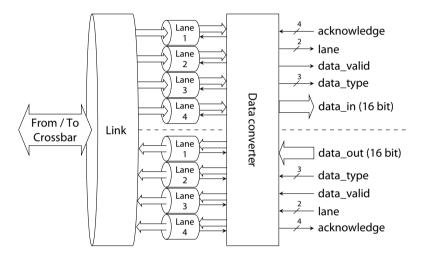

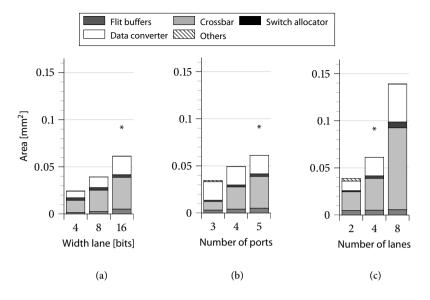

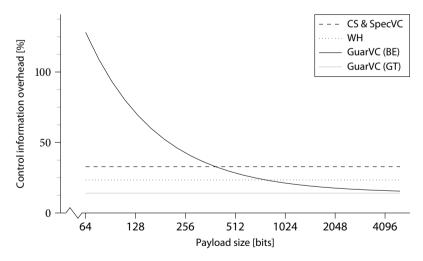

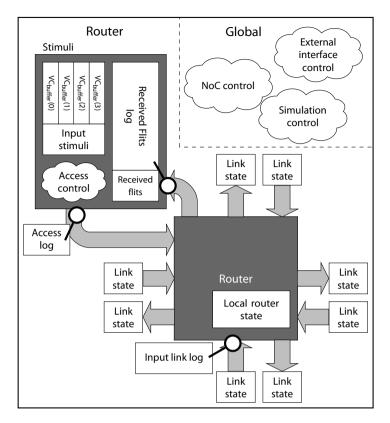

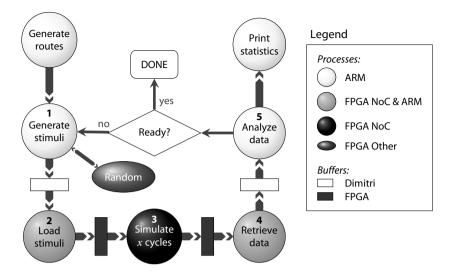

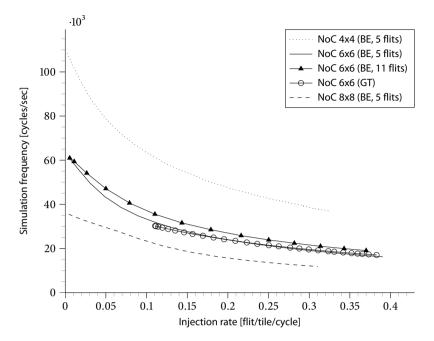

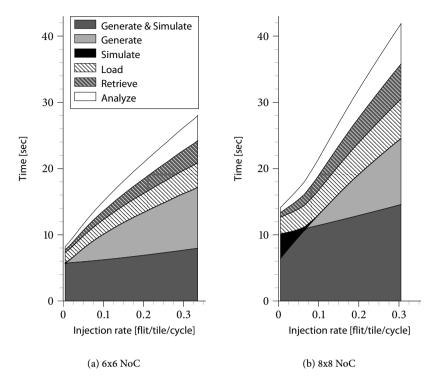

FIGURE 2.2 - Examples of regular topologies